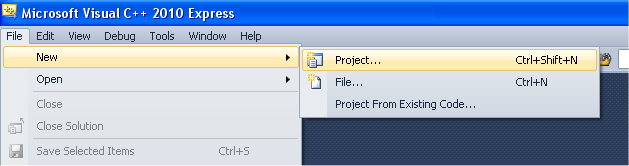

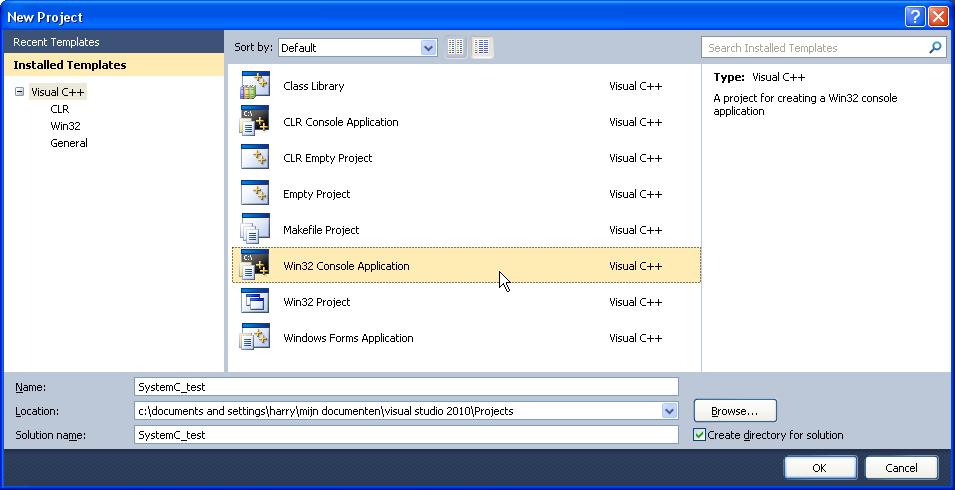

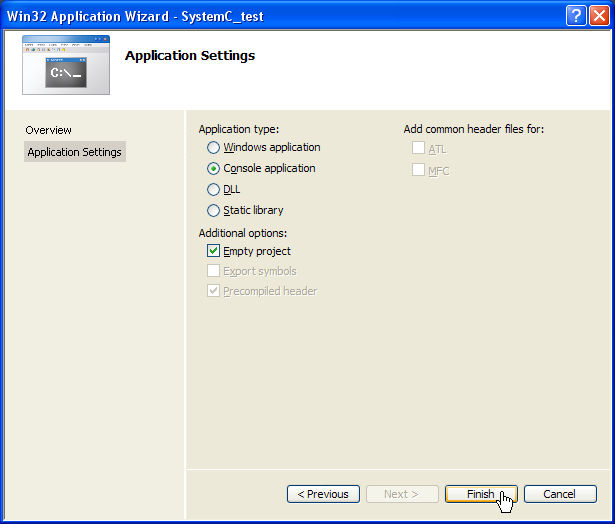

Kies Empty Project.

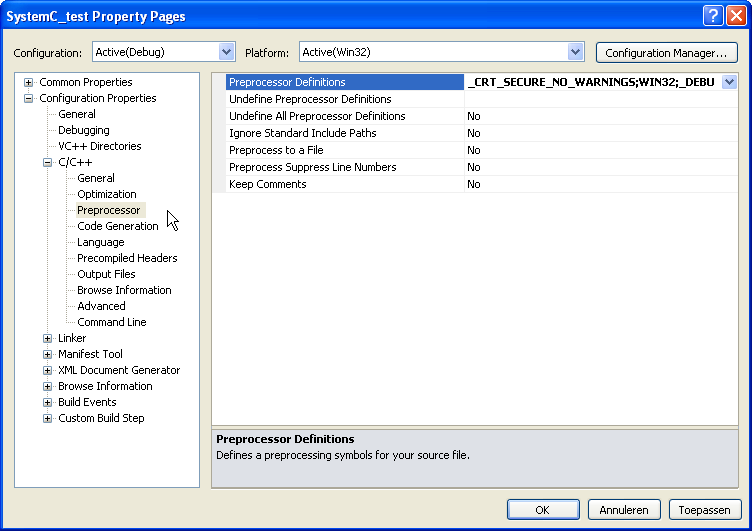

_CRT_SECURE_NO_WARNINGS; Dit voorkomt dat

de Visual C++ compiler warnings geeft bij alle functies waar in de laatste

C standaard (C11) zogenoemde veilige (secure) versies van zijn gedefinieerd.

Zie eventueel hier:

Secure string

functies in C11.

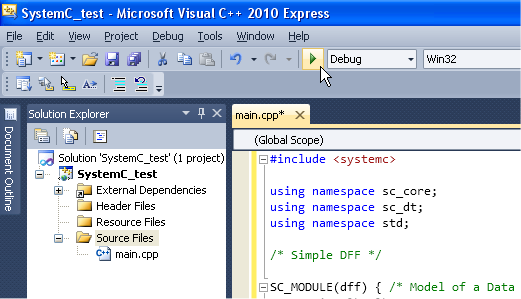

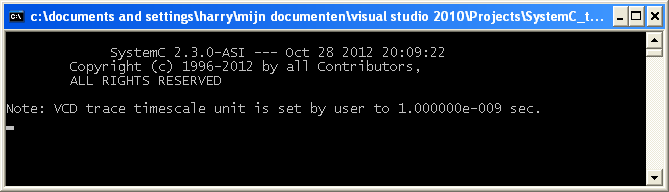

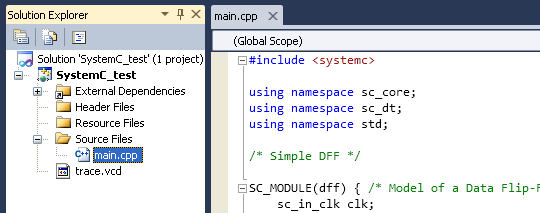

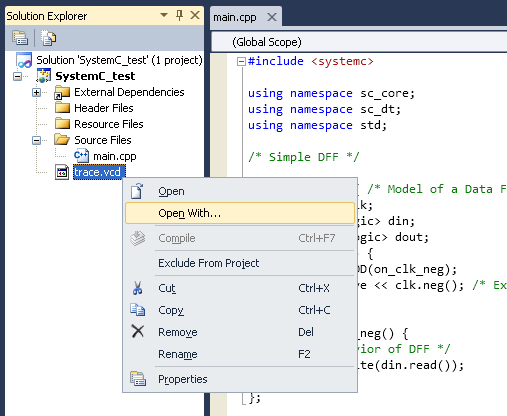

#include <systemc>using namespace sc_core;using namespace sc_dt;using namespace std;/* Simple DFF */SC_MODULE(dff) {/* Model of a Data Flip-Flop that reacts on a negative edge of the clock signal clk */sc_in_clkclk;sc_in<sc_logic> din;sc_out<sc_logic> dout;SC_CTOR(dff) {SC_METHOD(on_clk_neg);sensitive << clk.neg();/* Execute process on_clk_neg on every negative edge of the clock signal clk */}private:void on_clk_neg() {/* Behavior of DFF */dout.write(din.read());}};SC_MODULE(tb_dff) {/* Test bench for the DFF */sc_clock clk;sc_signal<sc_logic> din;sc_signal<sc_logic> dout;SC_CTOR(tb_dff):clk("clk",10,SC_NS,0.5), DUT("dff") {

/* Connect test bench with DFF which is the device under test (DUT)*/DUT.din(din);DUT.dout(dout);DUT.clk(clk);SC_THREAD(main);}private:dff DUT;void main() {/* test script */din.write(SC_LOGIC_0);wait(31, SC_NS);din.write(SC_LOGIC_1);wait(42, SC_NS);din.write(SC_LOGIC_0);}};int sc_main(int argc, char* argv[]) {tb_dff TB("tb_dff");/* Trace (record) signals */sc_trace_file *tf(sc_create_vcd_trace_file("trace"));tf->set_time_unit(1, SC_NS);sc_trace(tf, TB.clk, "clk");sc_trace(tf, TB.din, "din");sc_trace(tf, TB.dout, "dout");sc_start(100, SC_NS);sc_close_vcd_trace_file(tf);cin.get();return 0;}

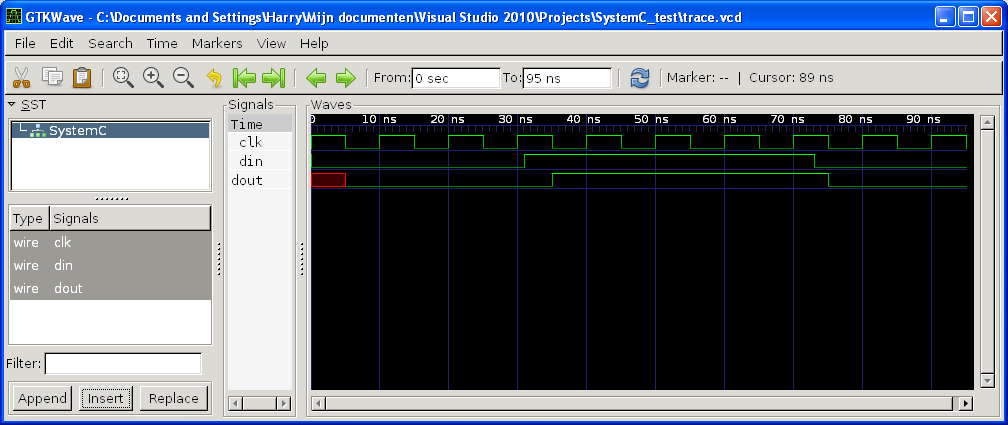

Dit is een low level (gate level) SystemC model van een

D

flip-flop. Dit is een eenvoudig geheugen-element. Het signaal op de ingang

din wordt alleen overgenomen op de uitgang dout

bij een negatieve flank op de clock ingang clk.